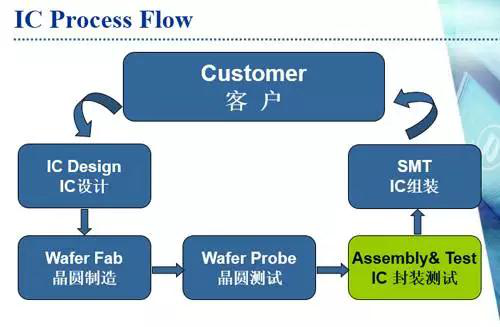

什么是IC封裝技術?

封裝技術是一種將集成電路用絕緣的塑料或陶瓷材料打包的技術。封裝對于芯片來說是必須的,也是至關重要的。因為芯片必須與外界隔離,以防止空氣中的雜質對芯片電路的腐蝕而造成電氣性能下降。另一方面,封裝后的芯片也更便于安裝和運輸。由于封裝技術的好壞還直接影響到芯片自身性能的發揮和與之連接的PCB(印制電路板)的設計和制造,因此它是至關重要的。

IC封裝技術發展的四個階段

第一階段:20世紀80年代以前(插孔原件時代)。

封裝的主要技術是針腳插裝(PTH),其特點是插孔安裝到PCB上,主要形式有SIP、DIP、PGA,它們的不足之處是密度、頻率難以提高,難以滿足高效自動化生產的要求。

第二階段:20世紀80年代中期(表面貼裝時代)。

表面貼裝封裝的主要特點是引線代替針腳,引線為翼形或丁形,兩邊或四邊引出,節距為1.27到0.4mm,適合于3-300條引線,表面貼裝技術改變了傳統的PTH插裝形式,通過細微的引線將集成電路貼裝到PCB板上。主要形式為SOP(小外型封裝)、PLCC(塑料有引線片式載體)、PQFP(塑料四邊引線扁平封裝)、J型引線QFJ和SOJ、LCCC(無引線陶瓷芯片載體)等。它們的主要優點是引線細、短,間距小,封裝密度提高;電氣性能提高;體積小,重量輕;易于自動化生產。它們所存在的不足之處是在封裝密度、I/O數以及電路頻率方面還是難以滿足ASIC、微處理器發展的需要。

第三階段:20世紀90年代出現了第二次飛躍,進入了面積陣列封裝時代。

該階段主要的封裝形式有焊球陣列封裝(BGA)、芯片尺寸封裝(CSP)、無引線四邊扁平封裝(PQFN)、多芯片組件(MCM)。BGA技術使得在封裝中占有較大體積和重量的管腳被焊球所替代,芯片與系統之間的連接距離大大縮短,BGA技術的成功開發,使得一直滯后于芯片發展的封裝終于跟上芯片發展的步伐。CSP技術解決了長期存在的芯片小而封裝大的根本矛盾,引發了一場集成電路封裝技術的革命。

第四階段:進入21世紀,迎來了微電子封裝技術堆疊式封裝時代。

它在封裝觀念上發生了革命性的變化,從原來的封裝元件概念演變成封裝系統。目前,以全球半導體封裝的主流正處在第三階段的成熟期,PQFN和BGA等主要封裝技術進行大規模生產,部分產品已開始在向第四階段發展。發行人所掌握的WLCSP封裝技術可以進行堆疊式封裝,發行人封裝的微機電系統(MEMS)芯片就是采用堆疊式的三維封裝。

IC封裝技術國內外對比

中國封裝技術與國外封裝技術的差距:

1.封裝技術人才嚴重短缺、缺少制程式改善工具的培訓及持續提高培訓的經費及手段。

2.先進的封裝設備、封裝材料及其產業鏈滯后,配套不全且質量不穩定。

3.封裝技術研發能力不足,生產工藝程序設計不周全,可操作性差,執行能力弱。

4.封裝設備維護保養能力欠偉,缺少有經驗的維修工程師,且可靠性實驗設備不齊全,失效分析(FA)能力不足。

5.國內封裝企業除個別企業外,普遍規模較小,從事低端產品生產的居多,可持續發展能力低,缺乏向高檔發展的技術和資金。

6.缺少團隊精神,缺乏流程整合、持續改善、精細管理的精神,缺少現代企業管理的機制和理念。

IC的封裝形式

IC Package (IC的封裝形 式)Package--封裝體:

?指芯片(Die)和不同類型的框架(L/F)和塑封料( EMC)形成的不同外形的封裝體。

?IC Package種類很多,可以按以下標準分類:

●按封裝材料劃分為:金屬封裝、陶瓷封裝、塑料封裝

●按照和PCB板連接方式分為:PTH封裝和SMT封裝

●按照封裝外型可分為:SOT、SOlC、TSSOP、QFN、QFP、BGA、CSP等;

IC Package (IC的封裝形式)

●按封裝材料劃分為:

金屬封裝主要用于軍工或航天技術,無商業化產品;

陶瓷封裝優于金屬封裝,也用于軍事產品,占少量商業化市場;

塑料封裝用于消費電子,因為其成本低,工藝簡單,可靠性高而占有絕大部分金屬封裝的市場份額。

IC Package (IC的封裝形式)

●按與PCB板的連接方式分為:

PTH-Pin Through Hole,通孔式;

SMT-Surface Mount Technology,表面貼裝式。目前市面上大部分IC均釆カSMT式的。

IC Package (IC的封裝形式)

●按封裝外型可分為:SOT、QFN、SOIC、TSSOP、QFP、BGA、CSP等;封裝形式和工藝逐步高級和復雜

●決定封裝形式的兩個關鍵因素:

?封裝效率。芯片面積/封裝面積,盡量接近1:1;

?引腳數。引腳數越多,越高級,但是工藝灘度也相應增加:

其中,CSP由于采用了Flip Chip技術和裸片封裝,達到了芯片面積/封裝而積=1:1,為目前**級的技術;

IC Package (IC的封裝形式)

●QFN- -Quad Flat No-lead Package四方無引腳扁平封裝●SOIC- -Small Outline IC小外形IC封裝

●TSSOP- -Thin Small Shrink Outline Package薄小外形封裝●QFP- -Quad Flat Package四方引腳扁平式封裝

●BGA- -Ball Grid Array Package球柵陣列式封裝

●CSP- -Chip Scale Package芯片尺寸級封裝

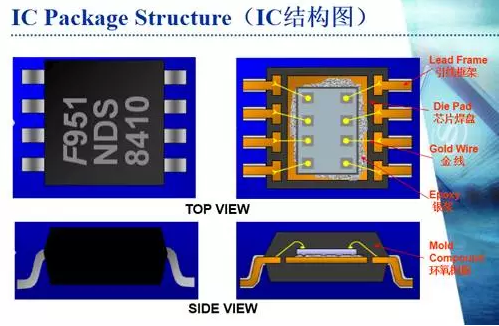

IC結構圖

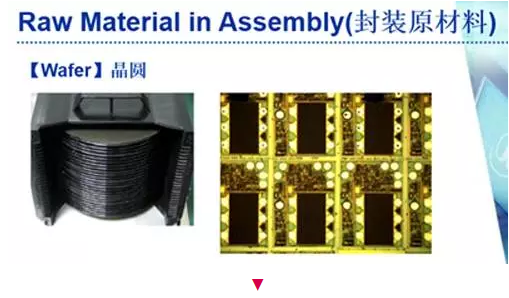

IC封裝原材料

前段工藝

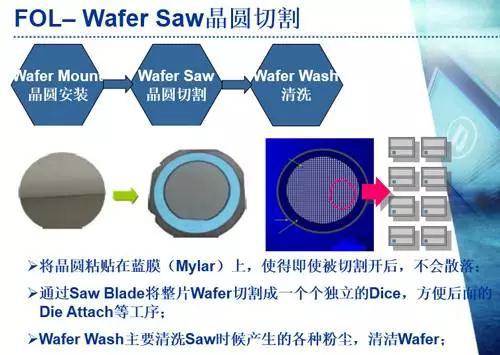

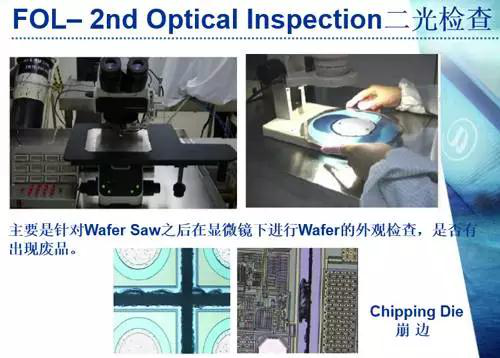

晶圓切割

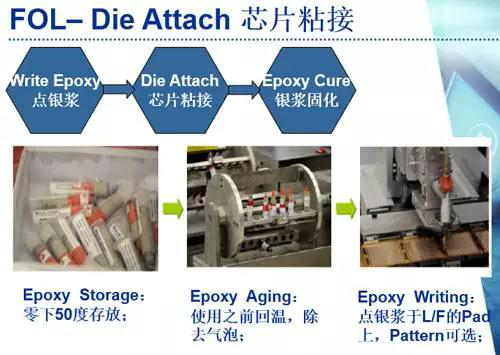

芯片粘接

引線焊接

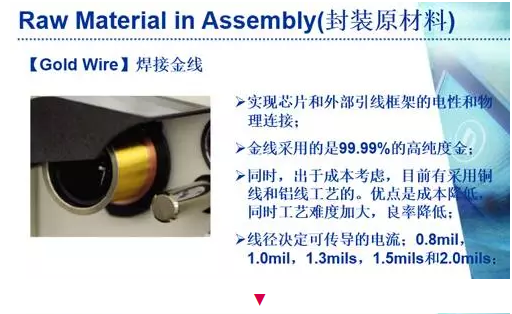

利用高純度的金線(Au)、銅線(Cu)或鋁線(AI) 把Pad

和Lead通過焊接的方法連接起來。Pad是芯片上電路的外接

點,Lead是Lead Frame上的連接點。

W/B是封裝工藝中最為關鍵的一部 工藝。

FOL- Wire Bonding引線焊接

Capillary:陶瓷劈刀。W/B 工藝中最核心的-個Bonding Tool,內部頭空心,中間穿上金線,并分別在芯片的Pad和Lead Frame的Lead上形成第一-和第二焊點:

EFO:打火桿。用于在形成第一焊點時的燒球。打火桿打火形成高溫,將外露于Capillary前端的金線高溫熔化成球形,以便在Pad上形成第一焊點(Bond Ball) ;

Bond Ball:第一-焊點。 指金線在Cap的作用下,在Pad 上形成的爐段,一般為一個球形; :

Wedge:第二焊點。指金線在Cap的作用下,在Lead Frame上形成的焊接點,一般為月牙形 (或者魚尾形) ;

W/B四要素:壓力(Force) 、超聲(USG Power)、時間(Time溫度(Temperature) ;

Wire Bond的質量控制:

Wire Pull、Stitch Pull (金線頸部和尾部拉力)

Ball Shear (金球推力)

Wire Loop ( 金線弧高)

Ball Thickness (金球厚度)

Crater Test (彈坑測試)

Intermetallic (金屬間化合物測試)

后段工藝

EOL-注塑-激光打字-高溫固化-去電鍍-電鍍退火-成型-第四刀光檢

注塑

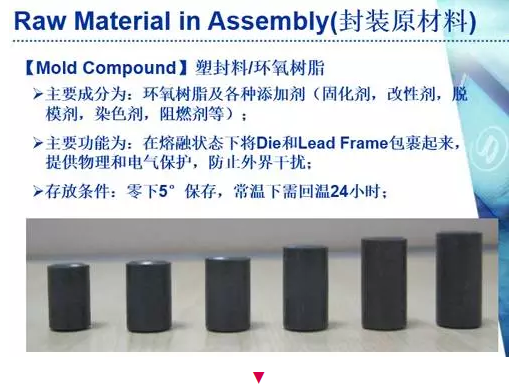

※為了防止外部環境的沖擊,利用EMC把Wire Bonding完成后產品封裝起來的過程,并需要加熱硬化。

?EMC (塑封料)為黑色塊狀,低溫存儲,使用前需先回溫。其物性為:在高溫下先處于熔融狀態,然后會逐漸硬化,最終成型。

?Molding參數:Molding Temp: 175~185°C; Clamp Pressure: 3000~4000N:Transfer Pressure: 1000~1 500Psi; Transfer Time: 5~15s;Cure Time: 60~120s。

-L/F置于模具中,每個Die位于Cavity中,模具合模。

-塊狀EMC放入模具孔中

-高溫下,EMC開始熔化,順著軌道流間Cavity中

-從底部開始,逐漸覆蓋芯片

-完全覆蓋包裹完生成型固化

激光打字

在產品(Package) 的正面或者背面激光刻字。內容有:產品名稱,生產日期,生產批次等:

模后固化

用于Molding后塑封料的固化,保護|C內部結構,消除內部應力。Cure Temp: 175+/-5° C; Cure Time: 8Hrs

去溢料

目的: De-flash的 目的在于去除Molding后在管體周圍Lead之間多余的溢料:

方法:弱酸浸泡,高壓水沖洗;

電鍍退火

目的:讓無鉛電鍍后的產品在高溫下烘烤一.段時間,目的在于消除電鍍層潛在的晶須生長(Whisker Growth)的問題;

條件: 150+/-5C; 2Hrs;

切筋成型

Trim:將一-條片的Lead Frame切割成單獨的Unit (IC) 的過程;

Form:對Trim后的IC產品進行引腳成型,達到T藝需要求的形狀,并放置進Tube或者Tray盤中:

第四道光檢

Final Visual Inspection-FVI

在低倍放大鏡下,對產品外觀進行檢查。主要針對EOL工藝可能產生的廢品:例如Molding缺陷,電鍍缺陷和Trim/Form缺陷等、

想了解更多日聯科技X-ray檢測裝備信息可以撥打全國服務熱線:400-880-1456 或訪問日聯科技官網:bigluo.com